The great explorer of the truth, the master-builder of human happiness no one rejects dislikes avoids pleasure itself because it is pleasure but because know who do not those how to pursue pleasures rationally encounter consequences that are extremely painful desires to obtain.

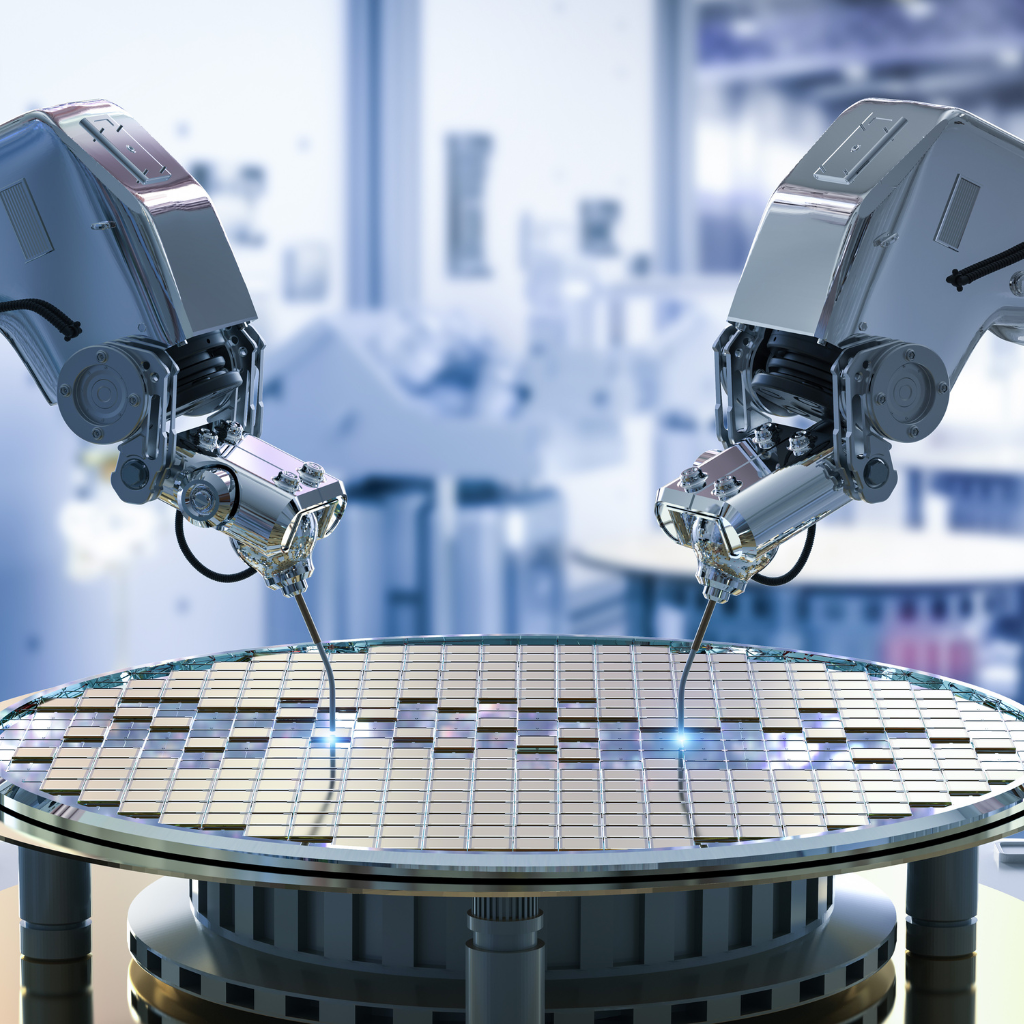

Read MoreCHIP DESIGN SERVICES

Our Chip Design Implementation Service is designed to help our clients design and implement high-performance chips. Our team of experts has years of experience in chip design, and we use state-of-the-art technology to ensure that our chips are of the highest quality. We work closely with our clients to ensure that their requirements are met and that the final product meets their expectations.

We offer comprehensive chip design services that encompass every stage of the design process. One critical aspect of our services is Architecture Specification, which lays the foundation for successful chip development.

The Architecture Specification phase is where ideas are transformed into tangible blueprints. Our experienced team collaborates closely with clients to define and refine the chip’s architecture, ensuring that it aligns perfectly with their unique requirements and goals.

With a meticulous approach, we analyze the application, performance targets, power constraints, and other key factors to craft a detailed architecture specification. This specification serves as a roadmap for the entire design process, guiding subsequent stages like RTL design, verification, and physical implementation.

Our expertise in architecture specification enables us to optimize chip performance, power efficiency, and overall functionality. We carefully balance trade-offs between different design parameters, identifying opportunities for innovation and differentiation. By leveraging our deep knowledge of the latest industry trends and emerging technologies, we ensure that the chip design is future-proof and adaptable to evolving market demands.

Throughout the Architecture Specification phase, we emphasize clear communication and collaboration, keeping clients informed and involved at every step. We value your input and insights, combining them with our technical expertise to create a design that exceeds expectations.

At GSME, we specialize in comprehensive chip design services that encompass every critical aspect of the design process. Our expertise extends to RTL CODING, INTEGRATION, AND VERIFICATION, ensuring seamless execution and delivering excellence in chip development.

Partnering with GSME for RTL Coding, Integration, and Verification means gaining access to a team of experts committed to excellence. We prioritize effective communication and collaboration throughout the process, ensuring that your input is valued and incorporated into the design.

Our experienced team excels in Register Transfer Level (RTL) Coding, where we transform architectural specifications into a hardware description language (HDL) code. With meticulous attention to detail, we create efficient and optimized RTL designs that form the backbone of the chip.

Seamless integration is vital for the success of any chip design. Our experts handle the complex task of integrating various RTL components, IPs (Intellectual Properties), and third-party modules into a cohesive system. We meticulously ensure compatibility, functionality, and performance across all integrated elements.

Thorough verification is critical to ensure the functionality and reliability of the chip. Our dedicated verification team utilizes advanced methodologies, including simulation and formal verification techniques, to validate the design against the specified requirements.

We provide comprehensive chip design services that encompass every crucial aspect of the design process. Our expertise extends to DFT (Design for Testability) and Synthesis, two essential components that drive efficiency and success in chip development.

With our focus on efficiency and quality, we streamline the DFT and Synthesis phases to accelerate time-to-market and minimize design iterations. Our expertise in DFT and Synthesis enables us to deliver chips that meet or exceed your expectations, while also ensuring manufacturability and testability.

Partnering with GSME for DFT and Synthesis means gaining access to a team of experts committed to excellence. We prioritize effective communication and collaboration throughout the process, ensuring that your specific requirements and constraints are considered at every step.

Designing chips with testability in mind is paramount for ensuring reliable and efficient manufacturing processes. Our experienced team excels in implementing DFT methodologies, incorporating built-in test structures, and optimizing the design for easy and accurate testing. By leveraging advanced techniques like scan chains, boundary scan, and built-in self-test (BIST), we empower your chip with comprehensive testing capabilities, streamlining the manufacturing and validation processes.

The synthesis phase is a critical step in the chip design journey, where the high-level RTL (Register Transfer Level) description is transformed into a gate-level representation. Our skilled synthesis engineers utilize state-of-the-art tools and methodologies to optimize the design for area, power, and timing constraints. Through careful analysis and optimization, we ensure that your chip design achieves the desired performance targets while meeting power efficiency and area utilization goals.

We offer comprehensive chip design services that encompass every crucial stage of the design process. One essential aspect of our services is Place & Route, a vital step in chip development that ensures optimal chip layout and connectivity.

Our expertise in placement and routing methodologies enables us to meet or exceed your design goals while considering the specific constraints and requirements of your project.

With a focus on efficiency and quality, we streamline the Place & Route phase to accelerate time-to-market and minimize design iterations. Our commitment to effective communication and collaboration ensures that your input is valued and incorporated into the layout and connectivity decisions.

Partnering with GSME for Place & Route means accessing a team of experts dedicated to delivering optimal chip design. We leverage the latest tools and methodologies to achieve layout excellence, ensuring the seamless functioning of your chip.

The "Place" phase involves determining the ideal placement of various components, including standard cells, memories, and macros, on the chip's physical layout. Our experienced team utilizes advanced algorithms and methodologies to optimize the placement for factors such as timing, power, and area utilization. By strategically positioning components, we minimize signal delays, reduce power consumption, and optimize the chip's overall performance.

The "Route" phase is where we establish the interconnects between the placed components, creating the complex network that enables seamless data flow within the chip. Our experts employ state-of-the-art routing algorithms to generate efficient and reliable interconnects, considering factors such as timing constraints, signal integrity, and manufacturability. We ensure that the routing achieves optimal performance while adhering to design rules and standards.

We provide comprehensive chip design services that encompass every critical aspect of the design process. One essential phase of our services is Post Layout Verification, which plays a vital role in ensuring the accuracy and reliability of the chip design.

Post Layout Verification involves thorough analysis and validation of the chip’s physical layout after the placement and routing stages. Our experienced team utilizes advanced verification methodologies and tools to assess various aspects of the design, including timing, signal integrity, power integrity, and design rule compliance.

Through rigorous testing and analysis, we verify that the physical layout meets the design specifications, functional requirements, and industry standards. We identify and resolve any potential issues or violations that may arise during the layout process, ensuring that the final chip design is robust and reliable.

Our post-layout verification process includes timing analysis to ensure proper signal timing and avoid any potential timing violations. We also conduct extensive power integrity analysis to verify the power distribution network and identify any potential power-related issues. Additionally, we perform signal integrity analysis to ensure that the design meets signal integrity requirements and maintains signal quality.

With our focus on accuracy and reliability, we strive to deliver chip designs that meet or exceed your expectations. Our post-layout verification phase minimizes the risk of design errors and ensures a high-quality chip ready for manufacturing.

Partnering with GSME for Post Layout Verification means gaining access to a team of experts committed to excellence. We prioritize effective communication and collaboration throughout the process, ensuring that your specific requirements and constraints are considered in the verification process.

In chip design services, Physical Verification plays a crucial role in ensuring the integrity and manufacturability of the chip design.

At GSME, we offer comprehensive Physical Verification services to validate the design against fabrication constraints, design rules, and industry standards. Our experienced team utilizes advanced verification tools and methodologies to meticulously analyze the physical layout, identifying potential issues such as design rule violations, lithography concerns, and metal density problems.

By conducting thorough Physical Verification, we ensure that your chip design is optimized for successful fabrication, minimizing the risk of manufacturing errors and ensuring a smooth transition from design to production. Trust GSME for your Physical Verification needs and gain confidence in the integrity and manufacturability of your chip design.

In chip design services, Tape Out Sign-Off is a critical milestone that signifies the completion and readiness of the chip design for manufacturing.

At GSME, we offer comprehensive Tape Out Sign-Off services to ensure that your design meets the necessary requirements and is ready to be sent for fabrication. Our experienced team conducts rigorous checks and verification processes to validate the design against various parameters, including design rules, electrical specifications, timing constraints, and manufacturing constraints.

With our expertise and attention to detail, we ensure that your chip design is optimized, error-free, and prepared for a smooth manufacturing process. Partner with GSME for Tape Out Sign-Off and confidently move forward with your chip design knowing that it has been thoroughly reviewed and is ready for successful fabrication.